随着网络的飞速发展,处理器架构、分组处理策略以及路由器和交换机核心技术也获得长足发展,但鲜为人知的是,正是内存技术的发展促进了这些高级架构的完善。目前,内存的种类已由RAM、DRAM)、SRAM)和SDRAM发展到单倍、双倍乃至四倍速(QDR)RAM、SigmaRAM、低延迟(RL)RAM以及最新面世的快速循环RAM(FCRAM)。在此,缓存速率、同一存储段的循环时间等问题是设计工程师对内存进行选择中面临的难题,本文介绍面对多种可选方案,设计工程师应该如何考虑设计要求与内存特性的精确匹配。

近年来,每一代新型的WAN交换机和路由器采用的技术均与前一代技术截然不同。随着互联网从低增长率的语言传输流转向需求更高的数据流,网络对核心交换机/路由器的要求也与日俱增,这归结于光纤传输系统的迅猛发展。激光技术及其它器件的发展使得传输设备提供商能使新一代核心网管道的带宽增大四倍。例如,WAN路由器在不到7年的时间内,已至少经历了两次飞跃发展,从OC-3到OC-192,再到OC-768。

各代产品之间性能的飞跃并不仅仅局限于器件部分。就其架构而言,由于互连距离限制了时钟速率,因此路由器和交换机的分离架构也被紧密封装盒(packed box)取代,封装盒内部全由智能线路卡构成,可完成大部分路由和转发操作。在某些架构中,交换结构位于每块智能线路卡上并通过无源底板互连,而其余架构则通过光学或电子中央交换结构与路由器和传输管理线路卡互连。架构变更的另一结果就是功率管理已成为当前和未来设计的首要任务。

随着业务提供商启动下一代网络,性能要求所需的技术飞跃已促使路由器和交换机的架构、分组处理策略和交换技术发生显著变化。然而,内存技术的更新还远远无法满足需求。虽然早期的路由器采用与服务器和工作站相同的存储策略(中央DRAM缓存),但在封装盒Sonet侧的线速率要采用较为昂贵的高速SRAM。因此,虽然PC业界的主流DRAM技术逐渐由单倍速(SDR) SDRAM转向双倍速(DDR) SDRAM,但WAN开发人员仍强烈拥护在数据通路处理中采用高速SRAM(如QDR 和SigmaRAM)。该转变源自PC-DRAM和SRAM之间的性能差异。

内存性能的评估

内存技术的性能一般根据WAN应用中的随机循环时间、延迟和块移动速率加以衡量。随机循环时间是指随机存取读或写之间的最短时间。延迟表征指令响应数据的滞后时间。块移动速率实际上不仅仅表示支持内部多组传输的内存突发速率,而且随数据块规格的增大,与数据引脚的原始位传输率(raw bit transfer rate)也很接近。比较两种主流内存类型的性能可见,当数据块规格增大时,133MHz DDR SDRAM的传输率可达每引脚266Mbps,且其随机循环时间tRC约为65ns。

相比之下,同等数目的167MHz QDR SRAM的传输率可达每引脚333Mbps,相应的tRC为12ns。这里采用的折衷是以密度为代价,换取5倍的循环时间性能。SRAM中的每位通常需要6个晶体管,而DRAM则只需一个晶体管和一个存储电容。注意到QDR SRAM的激励电流为450mA(此时Vdd=2.5V)。与以上提及的DRAM相比,该数值并未完全超出常规,但遗憾的是仅为SDR DRAM存储容量的1/16,即SDR DRAM的容量为32M字节,而QDR的容量仅为2M字节。

性能与容量的折衷在短期内是可接受的,因为设计工程师对速度更为关注。既然已达到OC-192速率,即输入数据流可以Gbps的速率传送净荷,那么还需要改变传输策略吗?

问题在于,路由器数据通路对内存容量的需求比速率更为迫切(图1)。例如,思科公司124系列互联网路由器中基于OC-192的SONET的分组传输(POS)线路卡采用了256M字节缓存来存储那些经过分类后仍无法经由快速路径路由的输入分组包。该缓存除了在交换架构之前可保存2,000个以上的业务队列外,还带有能在重传之前用于分组包重装的等规格后交换架构(post-switch fabric)传输缓存。

考虑输入端的线速率缓存要求,缓存器的带宽不仅要求足够快以支持全部线速率,还必须足够大以保存长度达到几十毫秒的分组数据。对于OC-192的线速缓存速率,这些计算即便不甚令人满意,其实现也极为容易。为支持9.953Gbps的原始突发速率,能保持每个DDR引脚的块传输速率达到333M至400M位的内存接口带宽至少为32位(舍入到最接近的字节数)。此外为使该缓存有效工作,还必须具有足够的读和写带宽,由于无法将速率提高一倍,因此接口带宽还必须增加一倍。

因此,总线时钟频率高达200MHz的输入端口缓存带宽必须达到64位。但其深度应当达到怎样的水平?这些执行方面的细节问题具体将取决于开发人员。然而,许多采用太位路由器的互联网业务提供商(ISP)需要高达100ms的缓存;有些甚至还要求达到300ms。如此庞大的缓存可在网络拥塞时通过提供高灵活性而使丢包率降至最低。

单个OC-192管道仅具有100ms的入口缓存容量,因而缓存需要9.6Gbps×0.10秒,约为120M字节。如果该架构在写模式和读模式之间需要反复缓存,那么上述数值将相应增大一倍。

因此,入口缓存可能需要带宽为64位的内存,以实现高达120M字节的缓存,或者入口缓存取决于读缓存器和写缓存器的管理模式。缓存容量需求可能促使设计工程师采用像PC-133这样的主流DRAM技术,但133MHz的SDR传送速率需要再次将缓存带宽增大一倍。其它的DRAM技术(如DDR SDRAM或Rambus)似乎更为适宜,但其60至70ns的随机循环时间仍是一个严重问题,因为在处理的分组数据中,50%以上是40字节的控制信息包。

SRAM缓存是解决上述性能问题的一种选择,但还需考虑其它问题。考虑到QDR SRAM的基本容量只为2M字节,因此100ms缓存器在OC-192速率上将需要60个部件。即便具有足够的线路板空间,完全实现上述内存配置所需消耗的功率也将达到70瓦。

新型网络内存

面向网络的FCRAM和低延迟DRAM (RLDRAM)有助于设计工程师克服与OC-192卡缓冲存储器设计相关的难题,其性能有利于设计工程师利用已掌握的DRAM知识,而这些知识可能源自为最低每位成本(cost-per-bit)应用所设计的产品。这些面向网络的新型DRAM专为高速数据应用精心打造,并改进了随机循环和块移动性能。

与其它基于DRAM的内存不同,这些新型的内存架构为设计工程师提供了完全时钟控制的输入和输出、块移动和以前只在高端SRAM中使用的随机循环时间。这些新型内存架构还提供高性能的刷新支持,解决内部存储段激活问题,消除循环之间的预加载时间,并为通信系统开发提供架构和封装。

目前,应用于PC中的PC266 DDR DRAM具有每引脚266Mbps的突发速率,且其随机存取时间为60或70 ns。网络DRAM的突发速率比PC DRAM高50%,而循环时间则不到PC DRAM的一半。尽管由于高端SRAM采用了更小的内存矩阵,其随机循环性能理应更好,但200MHz FCRAM的总体随机(非存储段或其它子类)循环时间(25ns)仅为167MHz QDR SRAM循环时间(12ns)的两倍。

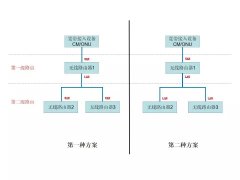

在许多应用中,由上述循环时间差异所提高的性能将因以下三种原因而被抵消:FCRAM具有16倍的密度、FCRAM支持同等的块移动速率,以及1:6的晶体管比率极大地降低了功耗。这些就是网络DRAM最初吸引太位路由器/交换机设计工程师的优良特性(图2)。

FCRAM中同一存储段的循环时间相当短,因此一旦管线始于交叉模式,那么理论上该传输就能持续进行,直至需要考虑其它因素(如刷新)。在128字节块传输示例中,FCRAM可提供比DDR存储器快25%的数据率,且随着数据块的增大(如支持1,500字节的IP分组数据),FCRAM的传送速率几乎是DDR的两倍。

但原始时钟速率并非衡量网络DRAM性能的唯一指标。在处理分组数据过程中,具有最短原始时钟速率的DRAM往往使系统承受最大的压力。NPU的实时性能通常可根据NPU处理背对背40字节TCP/IP控制信息包的能力加以衡量。由于控制信息包不需要连续配置在内存中,因此随机块存取的时间间隔与原始传送速率同样重要,而且对传输流所进行的研究也表明:混合数据中的一半是小分组数据包。

如果两个TCP/IP控制信息包在相同的PC-DDR存储段中背对背存取,由于存在较长的随机循环时间tRC,这两个块存取之间的间隔将达60至70ns。同样的问题也困扰着具有最高原始时钟速率(Rambus可达400MHz)的DRAM技术,这是导致DRAM技术难以得到广泛应用的一个重要原因。

相反,FCRAM能每25ns完成一次40字节数据块的随机存取。内存缓冲的平均性能更多的取决于随机循环而非突发速率和传统DRAM设计。与网络专用DRAM相比(图3和图4),传统的DRAM设计还存在一些缺陷。一些新型架构利用该性能优势,在查表应用中替代了SRAM和按内容寻址内存(CAM)。通过采用并行处理单元获取固定大小的数据块并保持数据总线繁忙,即可严格管理数据管线,进而在将线路板空间、成本和功耗降至最低的同时,保证最佳的内存性能。

各种内存的结构差异

在选择内存时,考察各种内存的不同架构相当重要。各种内存之间的主要区别在于阵列核心,因为每种DDR SDRAM均由四组8192行×512列的存储段构成,而FCRAM则由32768行×128列的存储段构成。FCRAM不支持8字节或半字节突发数据,但支持双倍速SDRAM。

设计工程师应当慎重选择内存,因为有时采用DDR SDRAM就已足够。例如,在对突发长度为8字节的单存储段进行读操作时,由于DDR SDRAM只需单个突发数据即可完成操作,而FCRAM则需要两个4字节的突发数据,因此DDR SDRAM更适用于这种特殊情形。如果该架构包含两个存储段操作,则应选用FCRAM,因其能更快地向第二个存储段发送读指令。

尽管这些特性使FCRAM和其它网络DRAM成为线速缓存的理想选择,但对于线路卡上的其它内存应用呢?如前所述,当前采用的10万条查表项达到100万条的时候,用于支持Cos/QoS/流量管理的队列也将变得极为庞大。

路由表查询

早期的几代路由表均建立在CAM的基础上,但由于存在规模问题,路由表已开始向基于DRAM的CAM(而非SRAM信元)转变,而且随着表项规模的不断增大,今后这种趋势将更加明显。为开发摆脱CAM规模限制的表项,一些开发人员采用了多层内存路由表构建方法。

在应用中,ASIC开发人员和NPU供应商均采用了网络DRAM的快速随机循环时间和块移动速率。这是路由逻辑电路以块或“大块”方式处理表项的常规设计方法,这里对每个数据块的存取完全是随机的。为优化表查询,可采用多个CPU对内存进行管线式存取,以使并行处理中表项和路由引擎间的数据传送达到最大。需要指出的是,该应用中的内存存储方法不同于先前讨论的线速缓存应用,后者由占空比为50%的随机读和写组成。

当然,当代网络DRAM不可能满足所有高速线路卡的内存要求,进而取代SRAM。SRAM还常用于像连接表(connection table)和链接表(linked table)这样的内存应用中。这些应用需要QDR随机循环时间, 或者完全不需要网络DRAM容量,尽管该容量在不断增长。虽然目前QDR的容量已足以应付这些应用,但下一代产品的容量要求还是促使设计工程师再次向网络DRAM开发人员寻求援助,以开发下一代40G产品或低成本的10G产品。

设计工程师正致力于采用DRAM技术提供与QDR相当的随机循环时间,以在降低功耗的同时极大地提高RAM架构的容量。这些努力有望于明年成为现实。事实上,延迟是网络DRAM无法与SRAM媲美的唯一性能特征,因为两者的常规存储段规格存在较大差异,但设计工程师完全可以借助RISC处理器管线处理功能弥补不足。

新型存储器产生的影响

近年来,WAN路由器和交换机开发人员被迫在各代存储器中进行重大的技术改造。各代存储器衔接点上的性能制约并非来自用户,而是来自ISP运营的核心网。遗憾的是,核心网偏离了快速发展的光传输轨道,而是转向发展Sonet。单单一项技术革新不足以保证下一代网络所需的性能飞跃,还需要得到片上系统ASIC技术、网络处理、微机电系统和光交换系统中高端技术的大力支持。架构变更及其相关问题(如密集分组数据包中的热生成)只会增大系统开发人员的开发难度。

这些具有DRAM技术固有的密度和功率优势的新型网络存储器可以有效地解决上述处理瓶颈。这些新产品不但能使原始数据吞吐率与高端SRAM相当,还缩短了两者之间循环时间和延迟的差异。此外,新产品还有助于设计工程师解决许多困扰SRAM或传统DRAM技术的难题。

设计工程师当然极力拥护将DRAM技术应用于高性能领域。尽管该技术推出的时间不长,但像仿真模型、ASIC控制器和FPGA控制器这样的宏支持架构已在许多产品中占有一席之地。广泛的应用领域本身就是一种产品支持。

目前,以更高的性能支持奇偶校验、错误检查和纠错架构的下一代产品已提上开发日程。网络DRAM技术不仅适用于最新一代的WAN路由器和交换机,还应用于低端设备中低成本的城域和边缘器件、快速演进的10G位以太网解决方案以及高端的OC-768解决方案中。